Completed

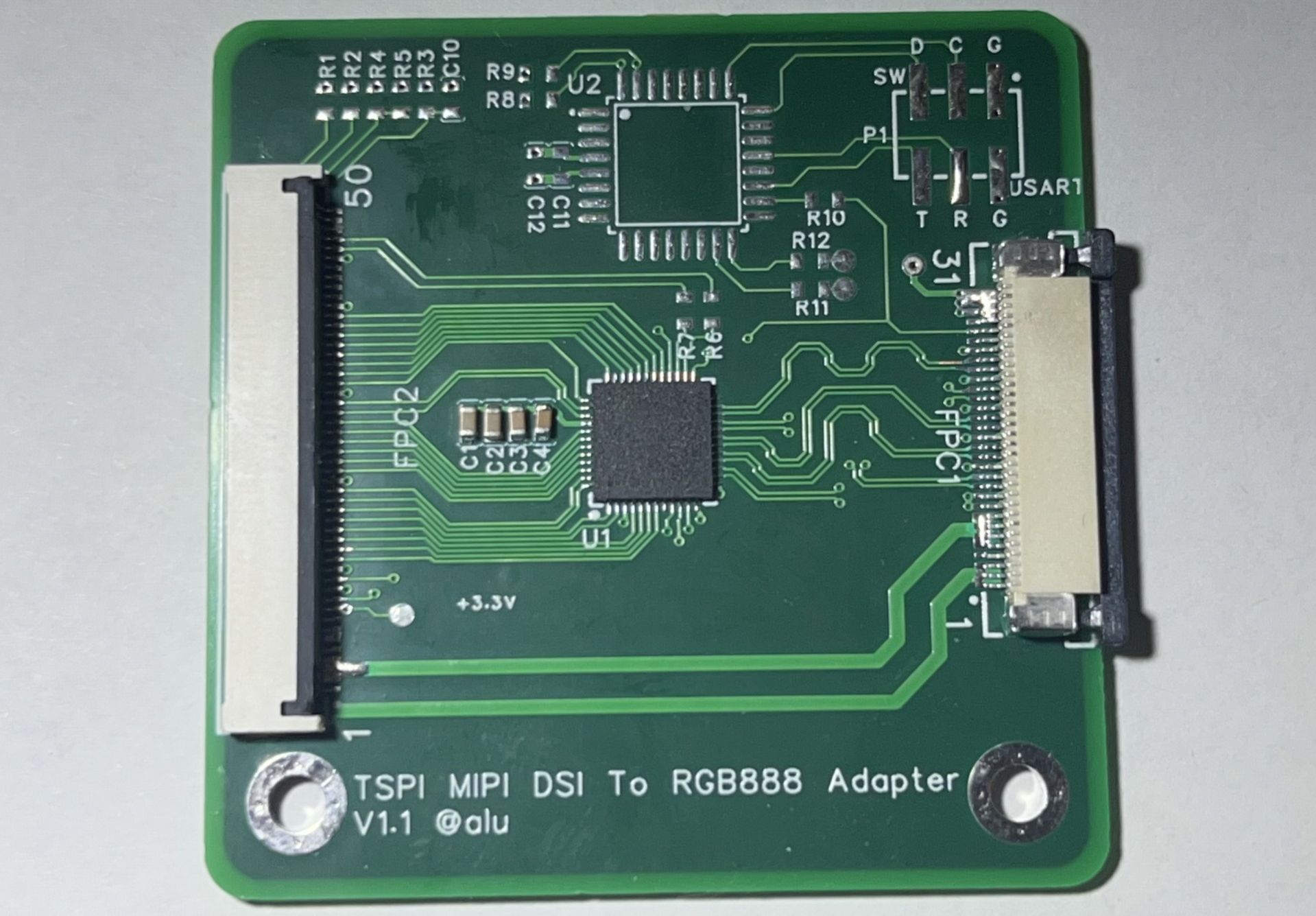

CompletedTaishan sends MIPI DSI to RGB adapter

PRO Taishan sends MIPI DSI to RGB adapter

Taishan sends MIPI DSI to RGB adapter

969

0

0

0

Mode:Full

License

:GPL 3.0

Creation time:2024-12-11 01:22:06Update time:2024-12-12 01:56:22

Description

Designed by okll (from OSHWHub)

Design Drawing

The preview image was not generated, please save it again in the editor.

The preview image was not generated, please save it again in the editor.Add to Album

0

0

Share

Report

Followers0|Likes0

Related projects

Empty

Empty

Comment